2018年开始,以中国芯片行业为代表的中国高科技产业受到了全面的封锁与打压。重压下的国人也在实现CPU芯片的自主可控,打破国外芯片在CPU芯片及指令集架构上的垄断,实现国产化。其中一项推动RISC-V指令集的国家指令集自主知识产权化的计划,希望用10年左右的时间,逐步完成开源芯片生态的建立,成为摆脱美国管制的一项重要武器。

RISC-V是一个开放的、免费的ISA,通过开放标准协作实现了处理器创新的新时代。RISC-V ISA诞生于学术界和研究领域,在架构上提供了一个新的自由、可扩展的软件和硬件自由水平。

RISC-V指令集是由加州大学伯利克分校的Andrew Waterman等人提出的一种新指令集。RISC-V在2015年成立了基金会,由200多个成员组织组成,建立了第一个开放、协作的软硬件创新者社区,为前沿创新提供动力。

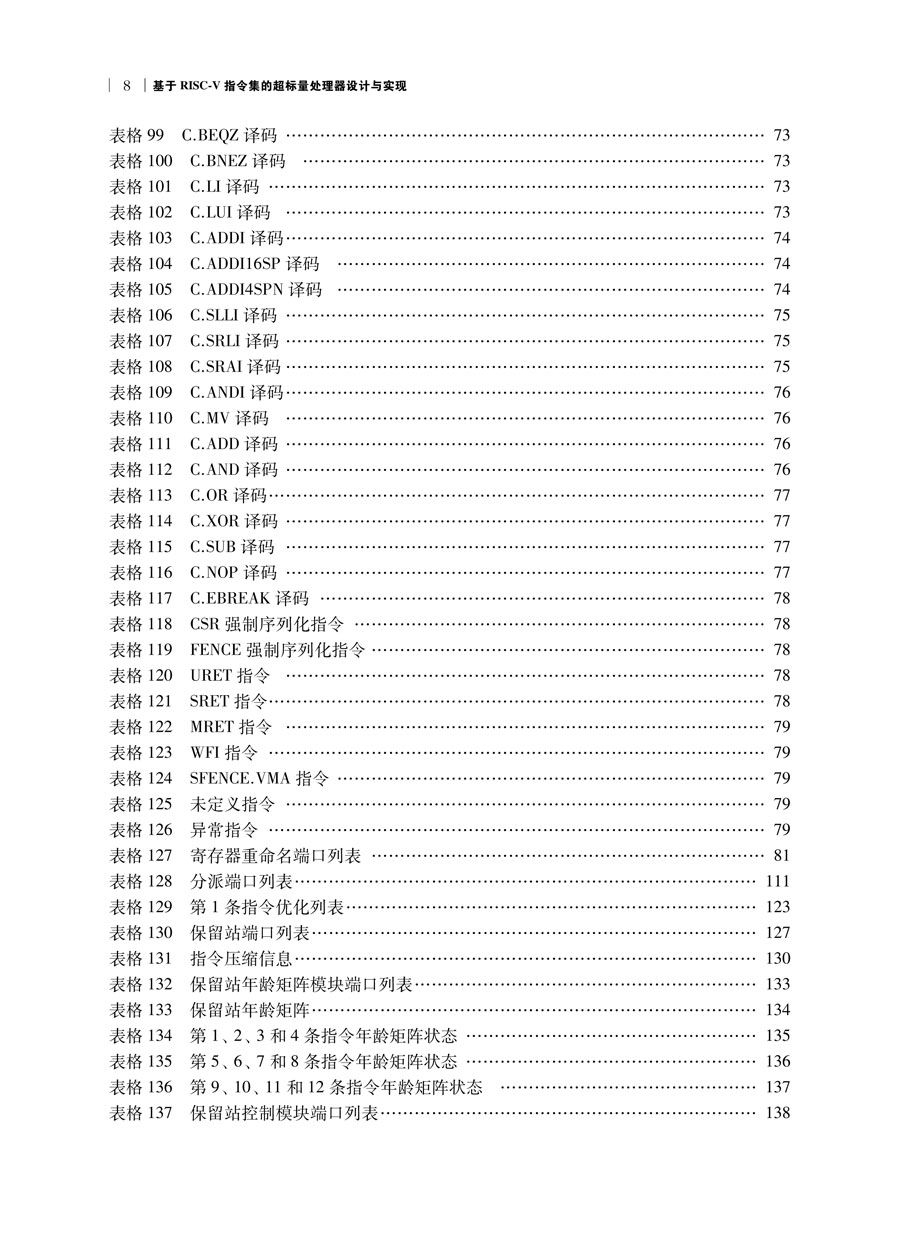

本书主要设计一个支持RV-32I、RV-32C和RV-32M指令集的超标量乱序执行处理器。该处理器的带宽为4发射,指令流水线深度为14级。流水线包括指令取指、分支预测、指令缓存、指令预处理、指令队列、指令译码、重命名、分派、保留站、执行单元、重排序及内存管理等模块。本书中讲述了每个模块的关键设计及实现逻辑。

温馨提示:请使用泸西县图书馆的读者帐号和密码进行登录